CMOS VS CCD, อะไรให้ภาพที่ดีกว่ากัน?

กระบวนการสร้างภาพและสถาปัตยกรรมควอนตัม

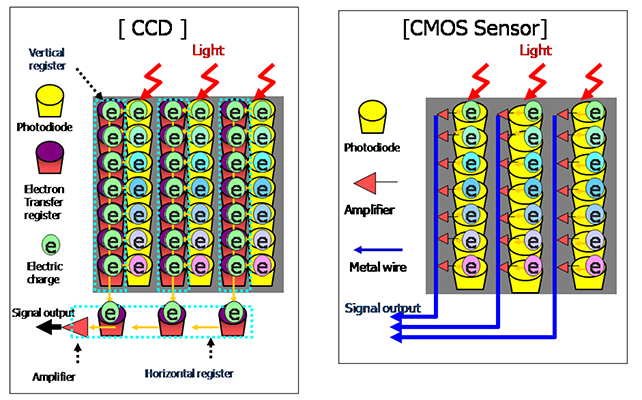

พื้นฐานแล้ว สถาปัตยกรรมออปติกทั้ง CMOS (Complementary Metal-Oxide-Semiconductor) และ CCD (Charge-Coupled Device) ทำการแปลงโฟโตอิเล็กทริกแบบขนาน—โดยเปลี่ยนการชนของโฟตอนในท้องถิ่นให้เป็นประจุอนาล็อกที่แยกจากกัน ความแตกต่างพื้นฐานของทั้งสองระบบทำงานอยู่ภายในส่วนการอ่านค่า (read-out) ของฮาร์ดแวร์โดยสิ้นเชิง

อาร์เรย์ CCD จะส่งแรงดันไฟฟ้าออกผ่านโหนดเอาต์พุตเดียวที่แยกออกมา (shift registers) ซึ่งรักษาการส่งสัญญาณแบบต่อเนื่องที่ไม่มีใครเทียบได้ โดยปราศจากการบิดเบือนของความแปรปรวน ในทางกลับกัน สถาปัตยกรรม CMOS แบบเฉพาะที่ (localized) จะเชื่อมโยงแอมพลิฟายเออร์สัญญาณโดยตรงกับทุกๆ อาร์เรย์ย่อยของพิกเซลทางกายภาพ โดยผสานรวมตรรกะเข้าไว้ในตำแหน่งนั้นๆ เลย แม้ว่าวิธีนี้จะทำให้ความสม่ำเสมอของสัญญาณสัมบูรณ์ลดลง แต่โหนดของ CCD ต้องการการจัดสรรแบนด์วิธความถี่สูงมากเกินไปสำหรับแอมพลิฟายเออร์ส่วนปลาย ในทางกลับกัน การฝังแอมพลิฟายเออร์แบบขนานเฉพาะที่ช่วยลดเกณฑ์การใช้พลังงานโดยรวมลงอย่างมาก อย่างไรก็ตาม การจัดการตัวรับส่งสัญญาณเฉพาะที่อิสระนับล้านตัว ย่อมเพิ่มจำนวนของ stationary distribution noise arrays มาตรฐานโดยธรรมชาติ—ซึ่งเป็นคอขวดทางอัลกอริทึมแบบคลาสสิกสำหรับการใช้งานสถาปัตยกรรม CMOS

2. ความหนาแน่นของการรวมแผ่น Wafer ทางกายภาพ

CCD มีต้นกำเนิดมาจากการจัดการสารกึ่งตัวนำแบบผลึกเดี่ยวโดยเฉพาะ การประมวลผลส่วนประกอบเหล่านี้ต้องใช้โหนดวงจรซิงโครนัสที่แตกต่างกันซึ่งทำงานบนโดเมนแรงดันไฟฟ้าที่หลากหลาย (ต้องใช้ analog decoders/imaging processors ที่แตกต่างกัน จัดเรียงตั้งฉากบนเมนบอร์ด) ซึ่งลดความหนาแน่นของความสามารถในการรวมวงจรลงอย่างมาก

ในทางกลับกัน ส่วนประกอบ CMOS มาตรฐานมีโปรไฟล์การผลิตที่เหมือนกัน ซึ่งผูกติดอยู่กับแม่แบบการประมวลผลตรรกะของ Integrated Circuit มาตรฐาน (เช่น โครงสร้างตรรกะของ CPU/SRAM) ด้วย "ดีเอ็นเอ" ที่ใช้ร่วมกันนี้ วิศวกรจึงสามารถวางส่วนปรับแต่งอนาล็อกเฉพาะที่ลงในเมทริกซ์หลักได้อย่างง่ายดาย สถาปัตยกรรม CMOS แบบ monolithic เพียงชิ้นเดียวสามารถรวม signal amplifier, ตารางการแปลง A/D (Analog-to-Digital) แบบขนาน และโหนด ISP controller ทางภาพเข้าไว้ด้วยกัน โมเดลการรวมวงจรบนชิปเดียวนี้เป็นปัจจัยสำคัญที่นำไปสู่ยุค "camera-on-a-chip"

3. วงจรความเร็วในการอ่านค่า

CCD ทำงานผ่านโปรโตคอลการจัดลำดับแบบ shift-register ที่เข้มงวด—โฟตอนจะถูกแปลงเป็นกลุ่มประจุไฟฟ้า โดยเรียงลำดับลงมาทีละบรรทัด ทำให้จำกัดอัตราเฟรมสูงสุด ระบบ CMOS ใช้ address decoders ที่มีความยืดหยุ่นสูง ทำให้สามารถสุ่มสำรวจข้อมูลเฉพาะที่ (localized high-speed polling vectors) ได้อย่างรวดเร็วโดยไม่มีความล่าช้าในการถ่ายโอนแนวตั้ง

สำหรับงาน forensic ในที่แสงน้อยมากๆ ที่ต้องการอาร์เรย์การสะสมแสงหลายวินาที พารามิเตอร์ของ CCD แบบดั้งเดิมจะเหนือกว่าข้อจำกัดของ CMOS มาตรฐาน ในการถ่ายภาพแบบ long-exposure สัญญาณรบกวนเฉพาะที่จะเกิดขึ้นภายใน registers ของ CMOS ทำให้ข้อมูลเสียหายอย่างรุนแรง

4. สถาปัตยกรรมสัญญาณรบกวน EMI

ในอดีต วงจร CCD ได้ทำการระงับการรบกวนทางแม่เหล็กไฟฟ้า (EMI) อย่างชัดเจนผ่านการฝังฉนวน PN-Junction ที่ทำจาก silicon dioxide (SiO2) อย่างแข็งแรง ซึ่งสร้างโครงสร้างภาพดิบที่ไร้ที่ติ เนื่องจากเลเยอร์ CMOS ทั่วไปจะบีบอัด analog converters ที่หนาแน่นไว้ติดกับ photoreceptors ที่ไวต่อแสงอย่างเคร่งครัด การรบกวนแบบ crosstalk จึงเป็นตัวกำหนดขีดจำกัดอย่างมาก การแทรกแซงด้วยซอฟต์แวร์เชิงอัลกอริทึมอย่างต่อเนื่องยังคงเป็นสิ่งจำเป็นเพื่อยกเลิกการรบกวนแบบคงที่ (static interference) ภายในโครงสร้าง CMOS ที่มีความหนาแน่นสูงทั้งหมด

5. ข้อจำกัดในการใช้งาน

เทคโนโลยี CCD ยังคงเป็นตัวกำหนดการทำแผนที่สเปกตรัมที่มีความเที่ยงตรงสูงแบบพิเศษ (Astro-telemetry และ biological microscopy) โหนดเหล่านี้เพิ่มประสิทธิภาพ quantum efficiency สูงสุดโดยใช้ข้อจำกัดของ dark currents แบบแยกส่วน

ในทางกลับกัน การใช้งาน Global Shutter CMOS ที่ซับซ้อน ได้เข้ามาเป็นส่วนสำคัญในงาน machine vision ที่มีความเร็วสูง เช่น การทำแผนที่ 3D-scanners และระบบสายพานอัตโนมัติ การใช้พลังงานต่ำที่เชื่อมโยงโดยตรงกับ independent row addresses ทำให้จำเป็นต้องมีการนำไปใช้ในอุปกรณ์ edge computation ที่ใช้แบตเตอรี่

ข้อมูลอ้างอิงจาก VisionMeta