เอาชนะ nRF24L01 ในสามขั้นตอน

การพิสูจน์หลักฐานการเชื่อมต่อแบบ Half-Duplex

โมดูล RF transceiver nRF24L01 รับประกันระยะการส่งสัญญาณที่เข้มข้นพร้อมกับการใช้พลังงานที่ต่ำ อย่างไรก็ตาม เมตริกที่กล่าวมานี้มักจะทำให้เกิดความล้มเหลวในการซิงโครไนซ์ที่สำคัญในการรวมระบบแบบกำหนดเองทั้งในระดับผู้ใช้งานทั่วไปและมืออาชีพ ข้อจำกัดหลักอยู่ที่เมทริกซ์การทำงานแบบ half-duplex โหมดการทำงานกำหนดการสลับที่เข้มงวดระหว่างสถานะการทำงานของ Rx (Receiver) และ Tx (Transmitter) ซึ่งต้องมีการ handshakes ของแพ็กเก็ต SPI ที่แม่นยำเพื่อระบุ ACKs (ขอบเขตการรับทราบ) ที่สำเร็จก่อนการล้าง buffer

บ่อยครั้งที่นักพัฒนาสันนิษฐานถึงการเชื่อมต่อแบบ dual-node full-function โดยไม่ได้แยกฟังก์ชันการทำงานพื้นฐานของ transceiver ออกมา สถาปัตยกรรมนี้ต้องการการแยก logic vectors ออกเป็นการทดสอบสามส่วนที่แยกจากกันและระบุได้ โดยเน้นที่ข้อจำกัดของ hardware และระดับสูงสุดของสัญญาณรบกวน

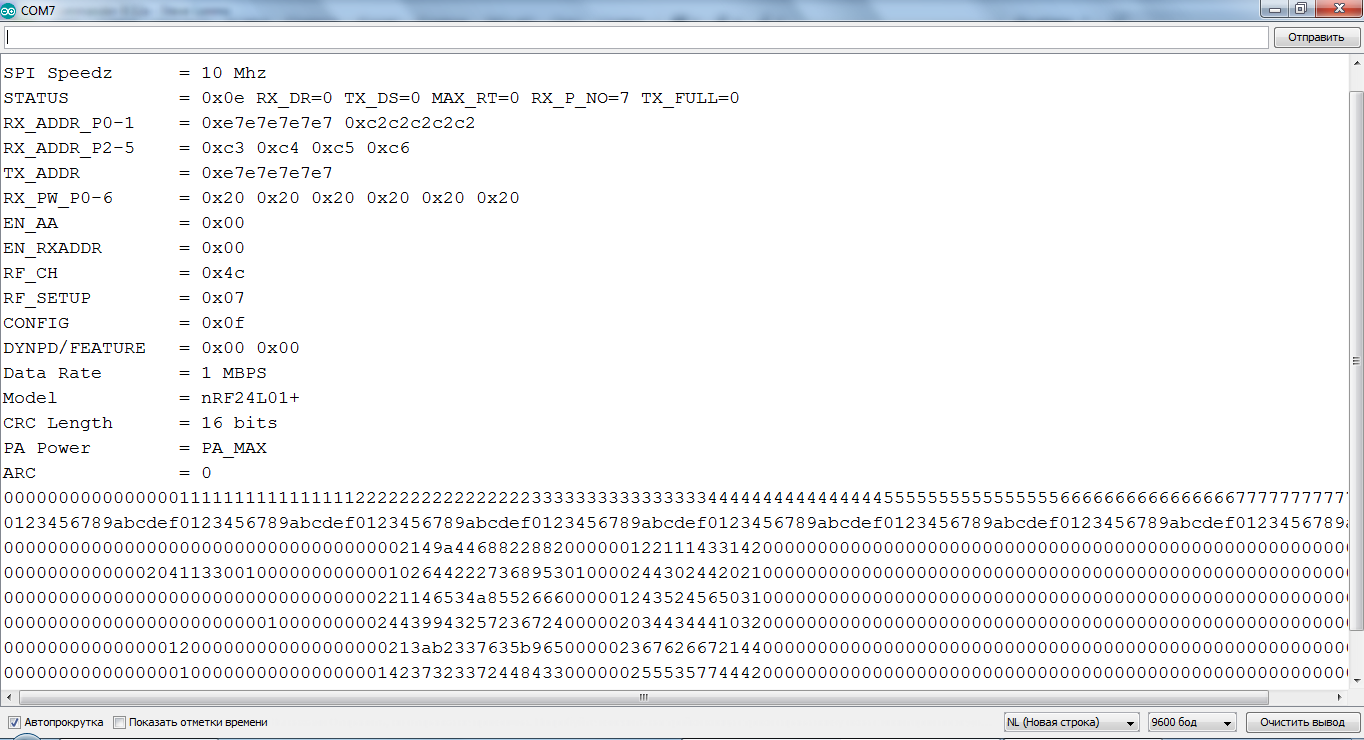

ขั้นตอนที่ 1: การสแกน Ether Node

ก่อนที่จะพยายามสร้างการเชื่อมต่อแบบ active handshake ระหว่าง nodes ที่แตกต่างกัน สิ่งสำคัญอันดับแรกคือการตรวจสอบสถานะการทำงานของ silicon layout ผ่านโครงสร้าง Ether Scanner (ที่พบได้ใน RF24 library -> Scanner) โดยการขยายระยะเวลาการสแกน channel แบบแยกส่วนจากขีดจำกัดมาตรฐาน 128 µs เป็น 512 µs ทำให้สามารถตรวจจับ noise floors ได้สำเร็จมากขึ้นในสภาพแวดล้อมที่มีความหนาแน่น การระบุช่องสัญญาณ 2.4 GHz ที่มีการรบกวนน้อยที่สุด (เช่น การดันขีดจำกัดการทำงานให้สูงกว่า Channel 60 หรือ Hex 0x3C) ช่วยเพิ่มขีดจำกัดความต่อเนื่องของ ACK handshake ได้อย่างมาก พื้นที่ analog ที่มีสัญญาณรบกวนสูงจะทำให้เกิด dropped packets ทันที โดยไม่คำนึงถึงความสมบูรณ์แบบของ C++ SPI definitions

ขั้นตอนที่ 2: การตรวจสอบการส่งสัญญาณแบบทางเดียว

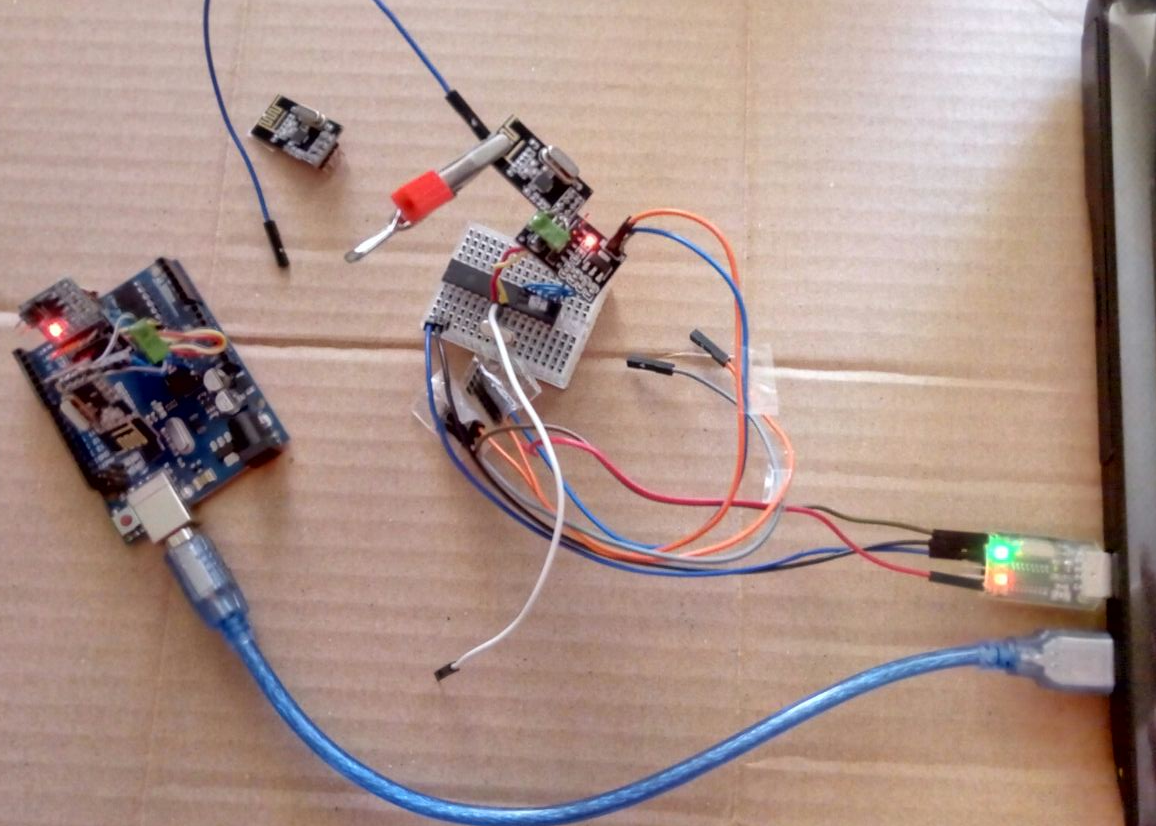

ประกอบ secondary node ที่ทำงานตาม single-state logic อย่างเคร่งครัด (unidirectional Transmitter vector) กำหนดให้ payload ส่งออกไปยัง clean channel ที่คงที่และได้รับการยืนยันแล้ว (เช่น 112 / 6f) ในขณะเดียวกัน ให้สังเกต primary node (ซึ่งทำหน้าที่เป็น ether scanner อย่างเคร่งครัด) ที่พยายามค้นหา hex anomalies ที่คงที่ซึ่งตรงกับ output channel array ที่คุณกำหนดไว้ โดยไม่คาดหวัง ACKs จาก algorithmic ที่เป็นทางการ

ขั้นตอนที่ 3: การลดทอน Hardware และการกรองสัญญาณ

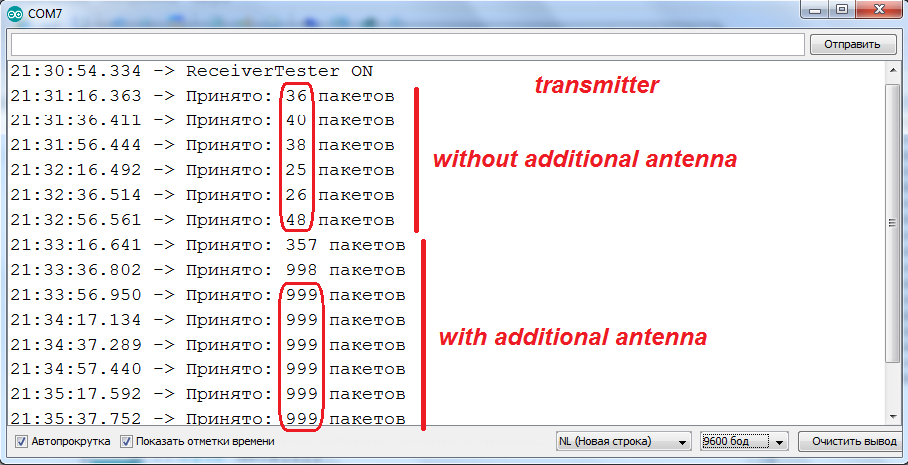

นี่คือจุดที่การทำงานเชิงตรรกะมักจะไม่สามารถชดเชยข้อจำกัดทางกายภาพได้ คุณอาจตั้งค่า C++ loop ที่สมบูรณ์แบบเพื่อจับแพ็กเก็ต 999 จาก 1000 แพ็กเก็ตได้ แต่หากขีดจำกัดการรับหยุดชะงักอยู่ที่ประมาณ 5% ของความจุเนื่องจากองค์ประกอบทางกายภาพที่มองไม่เห็น การลดทอน abstraction ของโค้ดก็จะไม่ทำให้เกิดการปรับปรุงใดๆ

- Antenna Redundancy: การขยายเสาอากาศ PCB แบบฝังภายในด้วย coaxial output array ขนาด 50 ohm ที่คำนวณอย่างแม่นยำและเชื่อมต่อขนานโดยตรงกับ pin

ANT2ช่วยปรับปรุง geometric RF mapping vectors ได้อย่างมาก - Analog Shunt Topologies: จุดที่ล้มเหลวที่สำคัญที่สุดอยู่ที่ rail step-down 3.3V ที่มีสัญญาณรบกวน ซึ่งสร้างขึ้นจาก Arduino regulators ดั้งเดิม ใช้ heavy parallel capacitance ระหว่าง header

VCCและGNDที่อยู่ใกล้กับ logic nodes ของ nRF24L01 การเชื่อมต่อ high-pass4.7µF Ceramic Capacitorพร้อมกับ10µF Electrolytic Capacitorจะทำหน้าที่เป็นตัวดักจับสัญญาณรบกวนอย่างสมบูรณ์ ข้อจำกัดของ hardware นี้จะกำจัดสัญญาณรบกวน SPI ความถี่สูงจากการไหลย้อนกลับผ่าน power rails พร้อมทั้งปรับกระแส in-rush pulses ขนาดใหญ่ที่ต้องการในช่วงสถานะ TX burst กะทันหัน ซึ่งมักจะทำให้สถาปัตยกรรม Atmel ล้มเหลว