Arduino Portenta H7 เนี่ยมันจัดเต็มไปด้วยฟีเจอร์เพียบ แถมยังรันโค้ดของเราได้บนสองคอร์ที่แยกจากกัน แล้วเจ้าสองคอร์นี้ยังคุยกันเองได้อีกด้วย!

เวลาเราทำโปรเจคก็ต้องมีติดขัดกันบ้างแหละน้อง งั้นวันนี้พี่จะมาสอนวิธีใช้ Segger JLink ในการดีบักโค้ดที่รันอยู่บนทั้งสองคอร์ พร้อมกันเลย! ฮ่าๆ

ภาพรวมโปรเจค

โปรเจค "Portenta-Debug" นี้เป็นการลงมือทำจริงจังในเรื่อง Asynchronous Dual-Core Forensics และ JTAG-Trace Orchestration ด้วยการใช้พลังจากชิป STM32H7 ความแรง ทำให้ระบบสามารถดีบักคอร์ Cortex-M7 และ Cortex-M4 พร้อมกันได้เลย โปรเจคนี้จะเจาะลึกไปถึง Inter-Process Communication (IPC) Diagnostics โดยใช้ฮาร์ดแวร์ Segger J-Link ในการทำ real-time instruction-trace และ memory-forensics สิ่งที่โฟกัสในการบิลด์ก็คือ dual-instance IDE orchestration, USB-driver heuristics และ deterministic RPC-sync harmonics

ล้วงลึกเทคนิค

- Dual-Core Orchestration & JTAG Forensics:

- The M7/M4 Logic-Hub: สถาปัตยกรรมของ Portenta H7 มี Cortex-M7 480MHz และ Cortex-M4 240MHz การทำ forensics จะเกี่ยวข้องกับลำดับการบูตที่กำหนดได้ของคอร์ M4 ผ่านการเรียกฟังก์ชัน

bootM4()การวินิจฉัยจะโฟกัสที่ "Subsystem-Synchronization Heuristics" เพื่อให้แน่ใจว่าการเข้าถึงพื้นที่หน่วยความจำร่วมกันจะไม่ทำให้เกิด semaphore-collision harmonics หรือ bus-contention forensics - Hardware Trace-Analytics:

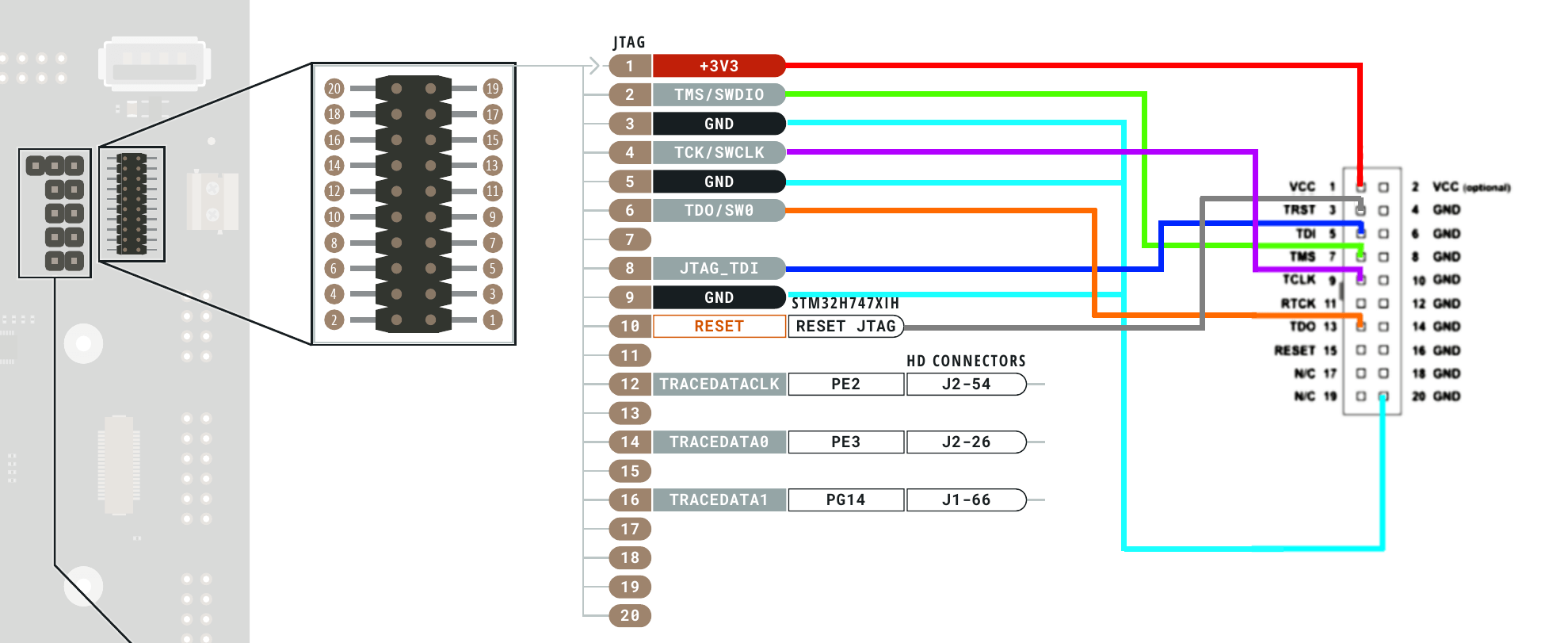

- J-Link SWD/JTAG Diagnostics: การทำ forensics เกี่ยวข้องกับการใช้ MIPS 20-pin adapter เพื่อเชื่อมต่อกับ debug-port ของชิป การวินิจฉัยจะเน้นที่ "Breakpoint-Persistence Analytics" ซึ่งจะอนุญาตให้นักพัฒนาสามารถหยุดการทำงานของคอร์ใดคอร์หนึ่งได้โดยอิสระ ในขณะที่ยังคงเก็บ telemetry ของ instruction-trace บนอีกคอร์หนึ่งไว้ด้วยความแม่นยำสูง

- The M7/M4 Logic-Hub: สถาปัตยกรรมของ Portenta H7 มี Cortex-M7 480MHz และ Cortex-M4 240MHz การทำ forensics จะเกี่ยวข้องกับลำดับการบูตที่กำหนดได้ของคอร์ M4 ผ่านการเรียกฟังก์ชัน

- Software-Hardening & Driver-Heuristics:

- Zadig USB-Driver Forensics: การตรวจสอบพอร์ตอนุกรมต้องการไดรเวอร์ที่มีลายเซ็นเฉพาะของ WinUSB หรือ LibUSB-win32 การทำ forensics เกี่ยวข้องกับการ remap Segger Interface 0 เพื่อให้แน่ใจว่ามีความเข้ากันได้กับ OpenOCD

- Visual Micro Debug-Orchestration: การทำ forensics เกี่ยวข้องกับการจัดการ Visual Studio สองอินสแตนซ์พร้อมกัน การวินิจฉัยจะเน้นที่ "Attach-to-Process" heuristics เพื่อให้แน่ใจว่า GDB-server จับคู่สัญลักษณ์ ELF กับพาร์ติชันหน่วยความจำทางกายภาพ (Flash/SRAM) ของชิป H7 ได้อย่างถูกต้อง

ตั้งค่าฮาร์ดแวร์

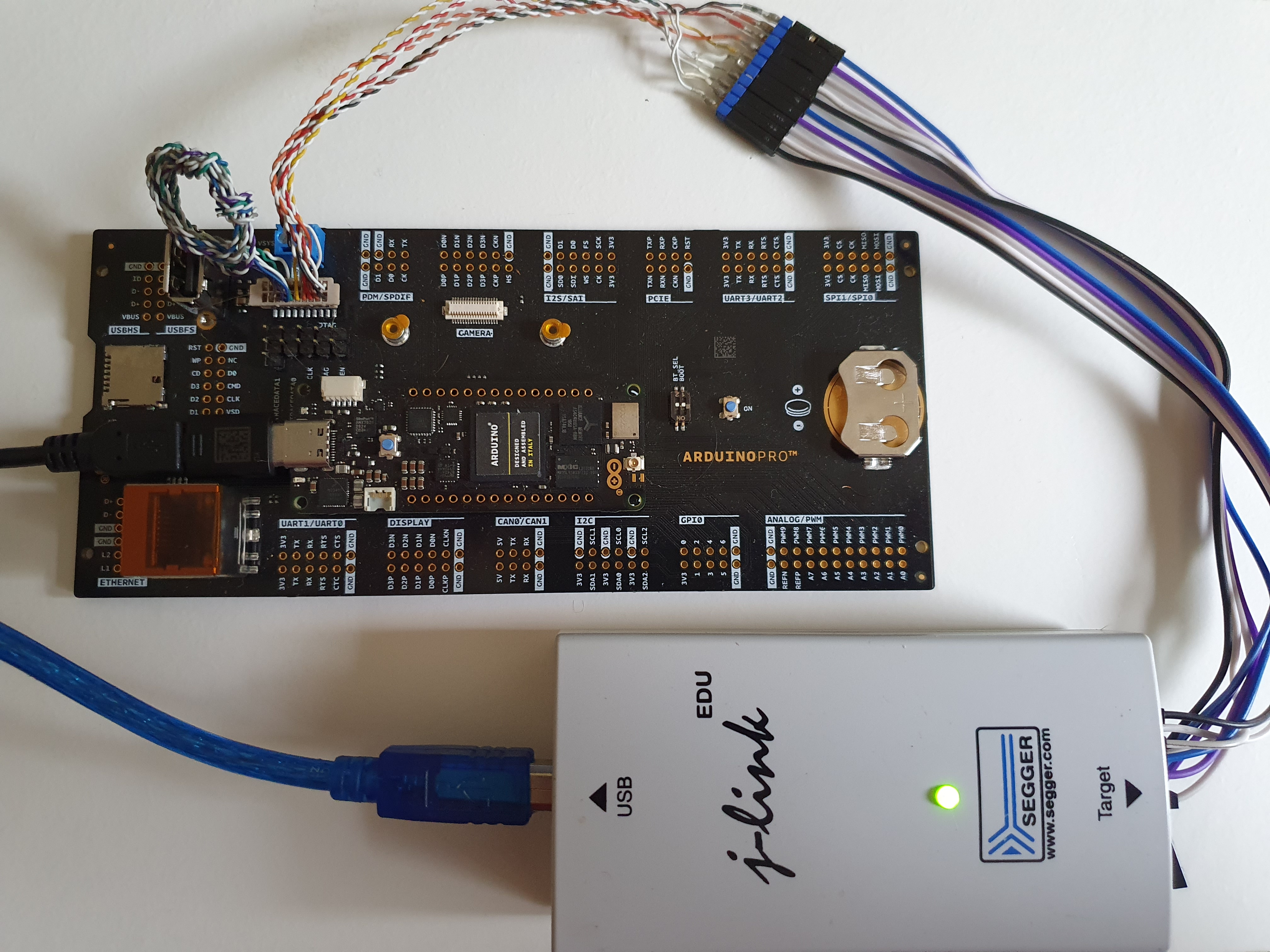

หลังจากที่น้องติดตั้ง Portenta H7 ของน้องลงบน breakout board แล้ว น้องจะต้องเชื่อมต่อ MIPS 20-pin converter ของน้องเพื่อแตกพินสำหรับดีบักออกมา

จากนั้นน้องก็สามารถเดินสายจาก converter ไปยัง Segger J-Link ได้ตามที่แสดงในภาพด้านล่างเลย

ถ้าน้องมีขาคอนเนคเตอร์ที่ถูกพิทช์ (0.05") น้องก็สามารถเดินสายทำคอนเนคเตอร์ของตัวเองได้ตามภาพที่สอง:

- Physical Connectivity & Signal-Integrity Forensics:

- PITCH-Interconnect Analytics: การดีบักที่ความถี่สัญญาณนาฬิกา JTAG 50MHz นั้นต้องการเส้นทางสัญญาณที่มีความเที่ยงตรงสูง การทำ forensics รวมถึงการใช้คอนเนคเตอร์พิทช์ 0.05" และสาย ribbon ที่มีความจุไฟฟ้าต่ำ การวินิจฉัยนี้จะทำให้แน่ใจว่า "Signal-Ringing Forensics" หรือ crosstalk จะไม่ทำให้เกิดการวินิจฉัยการรีเซ็ตฮาร์ดแวร์

- Breakout-Logic Diagnostics: การใช้ Portenta Breakout Board จะทำให้การเข้าถึงคอนเนคเตอร์ High-Density ง่ายขึ้น การทำ forensics จะเน้นที่ "Ground-Loop Mitigation" ระหว่างบอร์ดเป้าหมายกับหัววัด J-Link เพื่อรักษา harmonics ของระดับลอจิก

ตั้งค่าซอฟต์แวร์

เราถือว่าน้องติดตั้ง Arduino IDE ไว้แล้วในเครื่อง (ถ้ายัง ดาวน์โหลดตรงนี้)

จากนั้นติดตั้ง Visual Studio (2017/2019/2022) และส่วนขยาย Visual Micro ตามคู่มือเต็มๆ

น้องต้องติดตั้ง Board Package สำหรับ Arduino Mbed OS Portenta Boards จาก Visual Micro Explorer (หรือจาก Boards Manager ใน Arduino IDE) ด้วยนะ

สุดท้าย ต้องเปลี่ยน USB Driver บน Interface 0 ของ Segger J-Link ของน้อง โดยใช้เครื่องมือ Zadig.exe (ดูวิดีโอท้ายบทความประกอบได้)

มาเขียนโค้ดกันเถอะ!

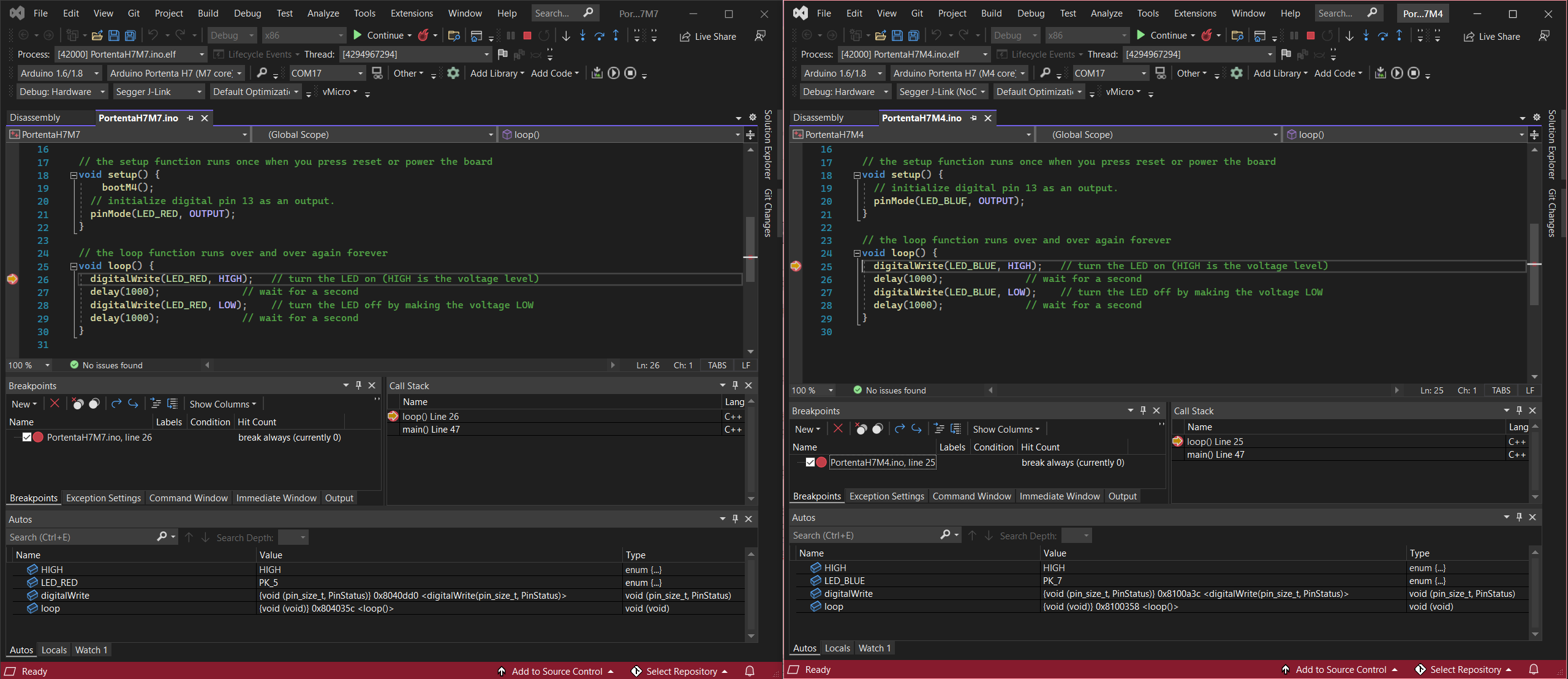

ทีนี้เราต้องตั้งค่าโปรเจคแยกกัน สำหรับแต่ละคอร์ของบอร์ด Portenta โค้ดตัวอย่างที่แนบมาเป็น Blink ง่ายๆ โดยแต่ละคอร์จะกะพริบ LED คนละสี สำหรับการดีบัก ให้ตั้งค่าแต่ละคอร์ใน Visual Studio คนละอินสแตนซ์

- RPC Synchronization & IPC Aesthetics:

- การนำไปใช้เน้นที่ "Asynchronous-Blink Aesthetics" ซึ่งแต่ละคอร์ขับ LED สีต่างกัน การวิเคราะห์เน้นที่ชั้น Remote Procedure Call (RPC) เพื่อบันทึกกระแสลอจิกที่จำเป็นสำหรับการแลกเปลี่ยนข้อมูลระหว่างคอร์อย่างเสถียร ในระหว่างการทำงานวินิจฉัยความเร็วสูง

อย่าลืมเรียกใช้ฟังก์ชัน bootM4() ในโปรเจคของ M7 Core เพื่อให้แน่ใจว่าทั้งสองคอร์ทำงานพร้อมกันนะ

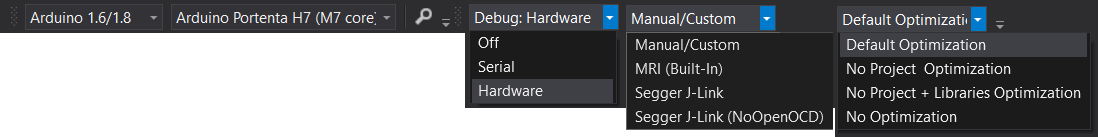

ตั้งค่าดีบัก: M7 Core

เปิด Sketch ของ M7 Core แล้วเลือก Debug > Hardware และเลือก Segger J-Link Debugger (ห้ามเลือกเวอร์ชัน "NoOpenOCD")

คอมไพล์และอัปโหลด Sketch ของ M7 ไปยัง M7 core ในขั้นตอนนี้

ตั้งค่าซอฟต์แวร์: M4 Core

เปิด Sketch ของน้อง แล้วเลือก Debug > Hardware และเลือก Segger J-Link Debugger (NoOpenOCD)

คอมไพล์และอัปโหลด Sketch ของ M4 ไปยัง M4 core ในขั้นตอนนี้

เริ่มดีบักเกอร์

เริ่มต้นดีบักโดยใช้ Sketch ของ M7 Core ก่อน ด้วยคำสั่ง "Debug > Attach to Process"

จากนั้นเริ่มดีบักโดยใช้ Sketch ของ M4 Core ด้วยคำสั่ง "Debug > Attach to Process" เช่นกัน

ตอนนี้น้องควรจะสามารถเพิ่ม breakpoint ลงใน Sketch ใดก็ได้ และดูดีบักเกอร์หยุดทำงานตรงนั้นได้แล้ว... โดยแต่ละคอร์สามารถหยุด/ก้าว/ดำเนินการต่อได้อย่างอิสระ!!

สรุป

Portenta-Debug คือสุดยอดแห่ง High-Performance Embedded Diagnostics การเชี่ยวชาญ Dual-Core Trace-Forensics และ JTAG-Orchestration Heuristics ในโปรเจคนี้ ส่งมอบเฟรมเวิร์กการดีบักระดับมืออาชีพที่แข็งแกร่ง ให้ความชัดเจนระดับซิลิกอนผ่านการวินิจฉัยระดับ aerospace ที่ซับซ้อน

Silicon Persistence: Mastering multi-core telemetry through JTAG forensics.

วิดีโอสอนแบบละเอียด

ดูวิดีโอสอนแบบละเอียดสำหรับขั้นตอนนี้ได้ด้านล่างเลยจ้า...

ลิงก์เด็ดๆ ที่ต้องมี

คู่มือ + ไดอะแกรมการต่อสาย (Documentation + Wiring Diagram) - เปิดดูได้เลย อย่าลืมอ่านก่อนลงมือต่อสายนะน้อง ไม่งั้นวงจรอาจจะไม่รอด!

บอร์ด Portenta Breakout - ของจำเป็นสำหรับคนที่อยากดึงพินทุกขุมของ Portenta มาใช้ ตัวช่วยชั้นดี!

Segger JLink - เครื่องมือดีบักระดับโปร ถ้าอยากลุยงานฮาร์ดคอร์แบบจริงจัง ตัวนี้ช่วยได้เยอะ